Rev. [6/2012] 6-19-2012

# **Table of Contents**

| 1 | Genero     | al Description                       | 5  |

|---|------------|--------------------------------------|----|

| 2 | Featur     | es                                   | 5  |

| 3 | Block D    | Diagram                              | 5  |

|   | 3.1 Signa  | l description                        | 7  |

|   | 3.2 VSIA i | interface                            | 9  |

|   | 3.2.1      | Write operation                      |    |

|   | 3.2.2      | Read operation                       |    |

|   | 3.2.3      | Reading from Status Register         |    |

| 4 | Protoc     | ol Management Block                  | 16 |

|   | 4.1 Introd | duction                              | 16 |

|   | 4.2 Interf | ace to UTMI                          | 16 |

|   | 4.3 USB P  | Packets Decoding                     | 18 |

|   | 4.4 Reset  | Signaling                            | 19 |

|   | 4.5 Suspe  | end and Resume signaling             | 20 |

|   | 4.6 USB 2  | 2.0 Test Mode Generation             | 21 |

| 5 | Enume      | ration Management block              | 22 |

|   | 5.1 Contr  | ol Endpoint Zero                     | 22 |

|   | 5.2 Enum   | neration Manager                     | 23 |

|   | 5.3 USB R  | Requests                             | 26 |

|   | 5.3.1      | Get Status Request                   | 26 |

|   | 5.3.2      | Get Configuration Request            | 28 |

|   | 5.3.3      | Get Interface Request                | 28 |

|   | 5.3.4      | Get Descriptor Request               | 29 |

|   | 5.3.5      | Set Address Request                  | 30 |

|   | 5.3.6      | Set Interface Request                |    |

|   | 5.3.7      | Set Configuration Request            |    |

|   | 5.3.8      | Set Feature Request                  |    |

|   | 5.3.9      | Clear Feature Request                | 33 |

|   |            | ptors                                |    |

|   | 5.4.1      | Device Descriptor                    |    |

|   | 5.4.2      | Device Qualifier Descriptor          |    |

|   | 5.4.3      | Configuration descriptor             |    |

|   | 5.4.4      | Other Speed Configuration Descriptor |    |

|   | 5.4.5      | Interface descriptors                | 37 |

|    | 5.4.6<br>5.4.7 | Bulk and Interrupt Endpoints Descriptors |    |

|----|----------------|------------------------------------------|----|

| 6  | Rulk IN er     | ndpoints                                 |    |

| U  |                | •                                        |    |

| 7  | Interrupt      | IN endpoints                             | 46 |

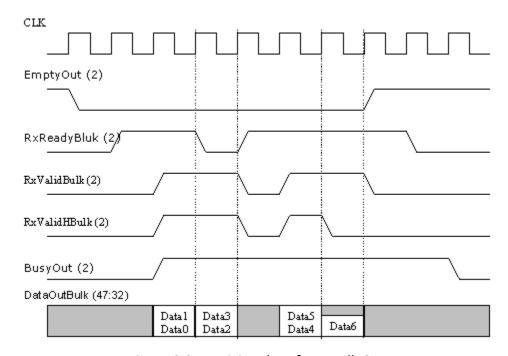

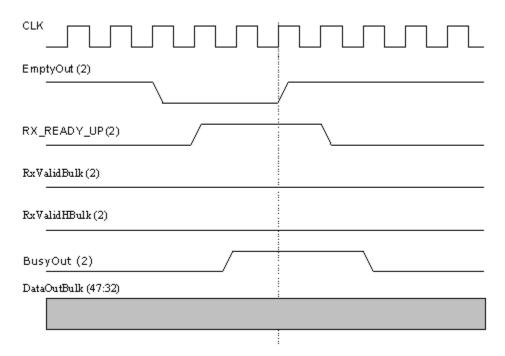

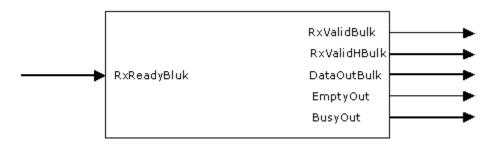

| 8  | Bulk OUT       | endpoints                                | 49 |

| 9  | Bulk zero      | endpoint                                 | 55 |

| 10 | Interru        | pt OUT endpoints                         | 56 |

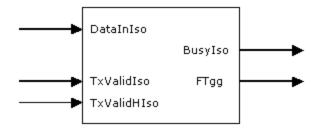

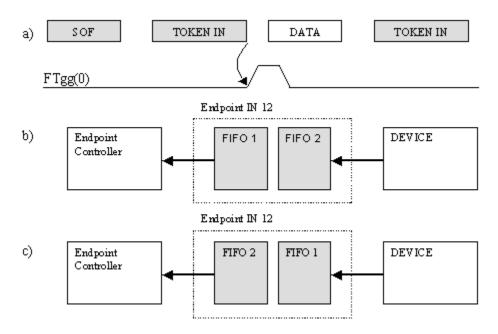

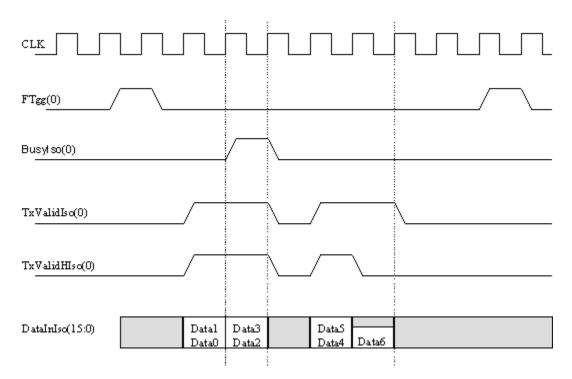

| 11 | Isochro        | nous IN endpoints                        | 60 |

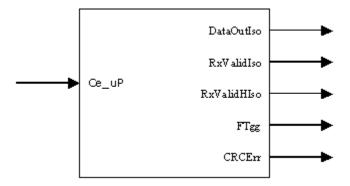

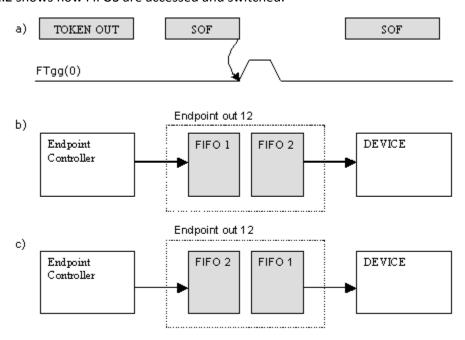

| 12 | Isochro        | nous OUT endpoints                       | 64 |

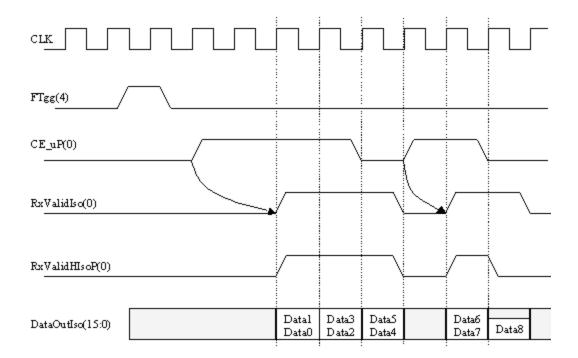

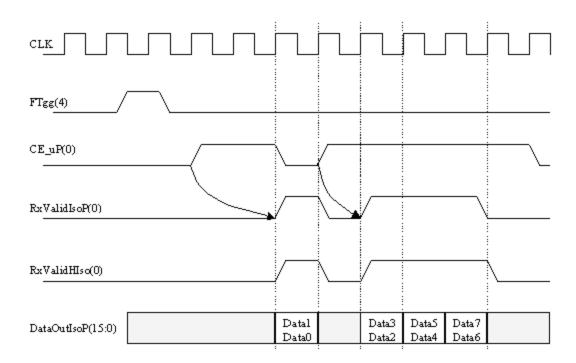

|    | 12.1 Isochro   | nous OUT endpoints interface             | 64 |

|    | 12.2 Debugg    | ing signals for ISO Out endpoints        | 69 |

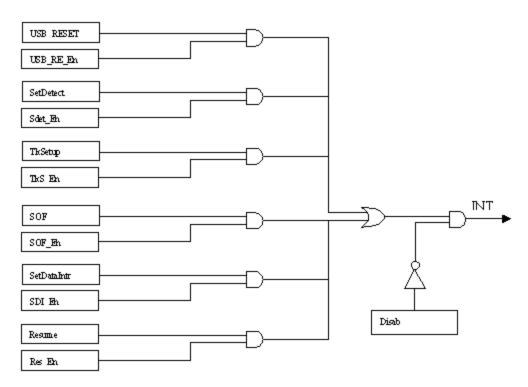

| 13 | Interru        | pts                                      | 70 |

| 14 | Registe        | prs                                      | 71 |

|    | 14.1 OUT0CI    | RTL register                             | 71 |

|    | 14.2 OUT1CI    | RTL register                             | 72 |

|    | 14.3 OUT2CI    | RTL register                             | 72 |

|    | 14.4 OUT3CI    | RTL register                             | 73 |

|    | 14.5 OUT4CI    | RTL register                             | 73 |

|    | 14.6 OUT5CI    | RTL register                             | 73 |

|    | 14.7 OUT6CI    | RTL register                             | 74 |

|    | 14.8 OUT7CI    | RTL register                             | 74 |

|    | 14.9 OUT8CI    | RTL register                             | 75 |

|    | 14.10 OUT90    | CRTL register                            | 75 |

|    |                | OCRTL register                           |    |

|    |                | ICRTL register                           |    |

|    |                | TL register                              |    |

|    |                | TL register                              |    |

|    |                | TL register                              |    |

|    |                | TL register                              |    |

|    |                | TL register                              |    |

|    |                | TL register                              |    |

| 14.19 IN6CRTL register                      | . 79 |

|---------------------------------------------|------|

| 14.20 IN7CRTL register                      | .79  |

| 14.21 IN8CRTL register                      | .79  |

| 14.22 IN9CRTL register                      | .80  |

| 14.23 IN10CRTL register                     | .80  |

| 14.24 IN11CRTL register                     | .81  |

| 14.25 Status Register                       | .81  |

| 14.26 DEVICE_addr register                  | .82  |

| 14.27 Test register                         | .82  |

| 14.28 Suspend register                      | .83  |

| 14.29 Interrupt Enable Register             | .83  |

| 14.30 New_Frm_L and New_Frm_L registers     | .83  |

| 14.31 Max Packet Size registers.            | .84  |

| 14.32 Setup registers                       | .85  |

| 14.33 Counter, WR and Counter, RD registers | 25   |

# **General Description**

Aldec USB 2.0 core is the RTL model of USB 2.0 Function Controller, which is fully compatible with the USB 2.0 specification. This core is available in VHDL along with behavioral testbench. The testbench gives code coverage at last 95% (statement, branch). The core has been optimized for popular FPGA devices and its functionality has been verified in the real hardware.

#### **Features**

- Fully compliant to USB 2.0 specification

- Supports full-speed 12Mbps and high-speed 480Mbps modes

- Supports USB 2.0 Transceiver Macrocell Interface (UTMI)

- Conformed to Virtual Component Interface Standard (VCI)

- Programmable number of endpoints

- Flexible endpoint configuration

- Support for bulk, interrupt and isochronous transfers

- Supports high-bandwidth mode

- Optionally maximum Packet Size for bulk, interrupt and isochronous endpoints

- Hardware enumeration manager

- Fully-synchronous design

- Interfaces to any application bus.

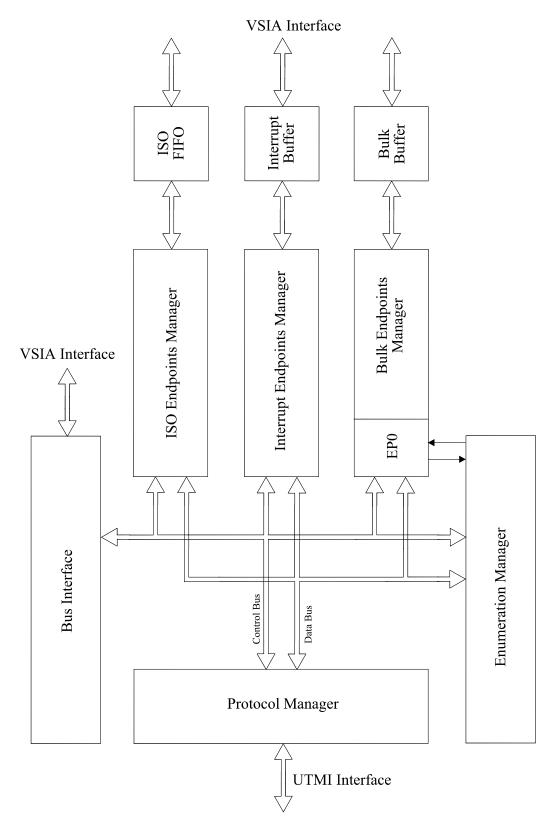

#### **Block Diagram**

The Protocol Manager is connected to UTMI transceiver. This module handles USB bus reset including high speed detection and suspend and resume signaling. The Protocol Manager handles token address decoding for USB packets. Each Endpoint Manager is informed by the Protocol Manager if a token addressed to the endpoint has been received. The Endpoint Managers handle communication between Protocol Manager and endpoint memory (Bulk/Interrupt Memory or Isochronous FIFO). Endpoint Managers handle ping protocol. The USB core contains additional module named Enumeration Manager. This unit handles the enumeration process when the device is first plugged in. The USB core handles all device requests over control endpoint zero, so the developer can immediately start writing code to transfer data over USB using these preconfigured endpoints. The Enumeration Manager can be turned off and the enumeration process may be handled by a microcontroller. Optionally, the Enumeration Manager may download firmware from USB host. The Bus Interface block provides interface between USB control registers and system bus. This interface is compatible with Virtual Component Interface Standard.

Figure 0.1 Simplified Block Diagram

# **Signal description**

All ports of ALUSB 2.0 core are described in following table.

| Pin name           | direction | description                                                                                        | Remarks                                           |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|---------------------------------------------------|

| CLK                | in        | System clock                                                                                       | Entire core is synchronized to rising edge of CLK |

| RESET              | in        | Asynchronous system reset                                                                          | Active high                                       |

| CLKEN              | in        | Global Clock Enable                                                                                | Active high                                       |

| DataIN(15:0)       | in        | Input data from UTMI                                                                               | See section 4.2                                   |

| RxActive           | in        | Receive Active – indicates that SYNC has been detected and UTM starts receiving data               | See section 4.2                                   |

| RxError            | In        | Error during receiving data                                                                        |                                                   |

| RxValid            | in        | Receive Valid – indicates that data on DataIn bus are valid                                        | See section 4.2                                   |

| RxValidH           | in        | Receive Valid – indicates that data on DataIn(15:8) bus are valid                                  | See section 4.2                                   |

| TxReady            | In        | Transmit Data Ready – indicates that UTM will load data from DataOut bus on the rising edge of CLK | See section 4.2                                   |

| LineState(1:0)     | In        | Line State – reflects the current state of the single ended receivers.                             | See section 4.2                                   |

| DataInISO(63:0)    | In        | Input Data to Isochronous endpoint                                                                 | See section 11                                    |

| Ce_up(3:0)         | In        | Read Strob for Isochronous endpoints OUT                                                           | See section 12                                    |

| TxValidHIso(3:0)   | In        | Strobe for writing higher byte of Isochronous IN endpoints                                         | See section 11                                    |

| TxValidIso(3:0)    | In        | Write strobe for Isochronous IN endpoints                                                          | See section 11                                    |

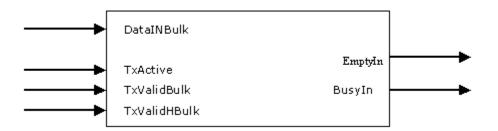

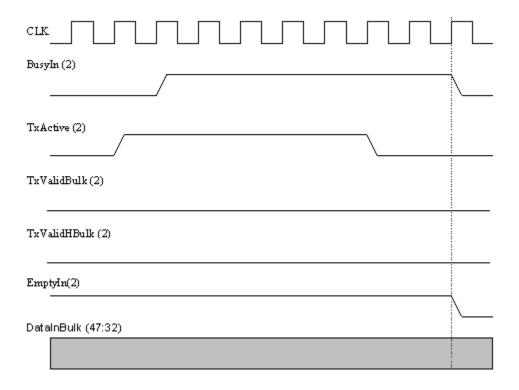

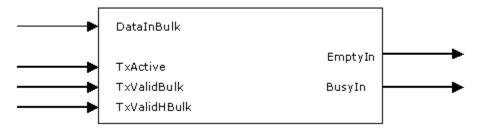

| DataInBulk(191:0)  | In        | Input data for Bulk endpints                                                                       | See section 6                                     |

| TxActive(11:0)     | In        | Data transfer to endpoint in progress                                                              | See section 6                                     |

| TxValidHBulk(11:0) | In        | Strobes for writing higher byte of input data                                                      | See section 6                                     |

| TxValidBulk(11:0)  |           | Strobes for writing lower byte of input data                                                       | See section 6                                     |

| RxReadyBulk(11:0)  | In        | External device ready for reading data from.                                                       | See section 6                                     |

| Wdata(7:0)         | In        | VSI input data                                                                                     | See section 3.2                                   |

| Addr(6:0)          | In        | VSI address                                                                                        | See section 3.2                                   |

| VAL                | In        | Valid strobe (VSI standard)                                                                        | See section 3.2                                   |

| WR                 | In        | Write strobe (VSI standard)                                                                        | See section 3.2                                   |

| DataExt(15:0)      | In        | Data from external descriptor's memory                                                             | See section 14.33                                 |

| DataOut(15:0)      | Out       | Output data for UTMI                                                                               | See section 4.2                                   |

| TxValid            | Out       | Strobe for transmitted data                                                                        | See section 4.2                                   |

| TxValidH           | Out       | Strobe for higher byte of transmitted data                                                         | See section 4.2                                   |

| OpMode(1:0)        | Out       | Operational Mode – select operation mode for UTMI transceiver                                      | See section 4.2                                   |

| TermSelect         | Out                                                                            | Termination Select – selects HS/FS termination.                           | See section 4.2       |  |  |

|--------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|--|--|

| XcvrSelect         | Out                                                                            | Transceiver Select – selects HS/FS transceiver.                           | See section 4.2       |  |  |

| SuspendM           | Out                                                                            | Suspend UTMI transceiver – macrocell circuitry drawing suspend current    | See section 4.2       |  |  |

| Suspend            | Out                                                                            | USB device is suspened                                                    | See section 4.2       |  |  |

| Resume             | Out                                                                            | USB device resumes its operation                                          | See section 4.2       |  |  |

| DataOutIso(63:0)   | Out                                                                            | Output Data from Isochronous endpoints                                    | See section 12        |  |  |

| RxValidIso(3:0)    | Out                                                                            | Strobe for data read from Isochronous OUT endpoints                       | See section 12        |  |  |

| RxValidHIso(3:0)   | Out                                                                            | Strobe for higher byte of data read from Isochronous OUT endpoints        | See section 12        |  |  |

| Busylso(3:0)       | Busylso(3:0) Out Isochronous In endpoints busy indicator                       |                                                                           |                       |  |  |

| Ftogg(7:0)         | Out                                                                            | Fifo toggle indicator of Isochronous endpoints                            | See section 12 and    |  |  |

|                    |                                                                                |                                                                           | See section 11        |  |  |

| PidErr(3:0)        | Out                                                                            | PID Error indicator of Isochronous Out endpoints                          | See section 8         |  |  |

| CrcErr             | Out                                                                            | CRC16 Error indicator of Isochronous Out endpoints                        | See section 8         |  |  |

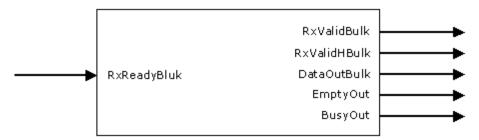

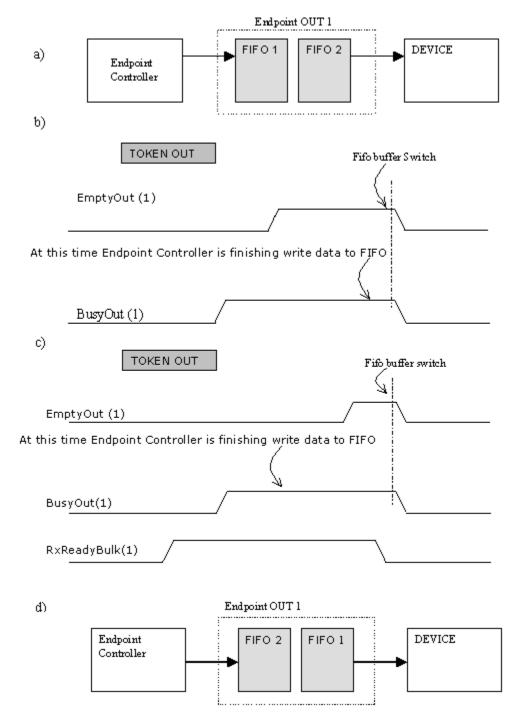

| DataOutBulk(191:0) | Out                                                                            | Output Data from Bulk out and Interrupt endpoints                         | See section 8         |  |  |

| RxValidBulk(11:0)  | /alidBulk(11:0) Out Strobe for data read from Bulk and interrupt OUT endpoints |                                                                           | See section 8         |  |  |

| RxValidHBulk(11:0) | Out                                                                            | Strobe for higher byte of data read from Bulk and interrupt OUT endpoints | See section 8 and     |  |  |

|                    |                                                                                |                                                                           | See section 9         |  |  |

| EmptyOut(11:0)     | Out                                                                            | Indicates that OUT endpoint is empty                                      | See section 8 and 9   |  |  |

| EmptyIN(11:0)      | Out                                                                            | Indicates that IN endpoint is empty                                       | See section 10 and 11 |  |  |

| Busyln             | out                                                                            | Indicates given IN endpoint is busy                                       | See section 10 and 11 |  |  |

| BusyOut            | Out                                                                            | Indicates given OUT endpoint is busy                                      | See section 8 and 9   |  |  |

| RData(7:0)         | Out                                                                            | VSI output data                                                           | See section 3.2       |  |  |

| AddExt(4:0)        | Out                                                                            | Address to external descriptor's memory                                   | See section 14.33     |  |  |

| INT                | Out                                                                            | Interrupt request signal                                                  | See section 3.2       |  |  |

| ACK                | Out                                                                            | Acknowledge signal (VSI standard)                                         | See section 3.2       |  |  |

| nUSBRes            | Out                                                                            | Reset for Kawasaki Transciever.                                           | See section 4.2       |  |  |

| REPEATNEEDED(3:0)  | Out                                                                            | Debug Signal for ISO OUT endpoints.                                       | See section 12.3      |  |  |

| REPEAT(3:0)        | In                                                                             | Debug Signal for ISO OUT endpoints.                                       | See section 12.3      |  |  |

## **VSIA** interface

The user can communicate with the ALUSB 2.0 via set of 8-bit registers assembled in table 3.1. The access to these registers is realized by simple 8-bit interface that is compatible to Virtual Component Interface (VCI) standard. The interface assures flexible connection to any other user IP, especially microprocessors and microcontrollers.

For clearance purpose, in this document, any device connected to the interface is called microprocessor.

The core utilizes 7 address lines. All registers occupy addresses from 00h to 67h.

Some registers are read-only, some write-only and some are read-write. Writing data to read-only or not implemented register does not affect specified register. Reading from write-only or not implemented register causes the read data is 00h.

Table 0.1 ALUSB 2.0 registers

| address | Name                                                                                                  | Description                                    | Dir |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|--|--|--|

| 00h     | OUT0CRTL                                                                                              | Sets toggle and resets Bulk0 OUT endpoint      | W   |  |  |  |

| 01h     | OUT1CRTL                                                                                              | Sets toggle and resets Bulk1 OUT endpoint      | W   |  |  |  |

| 02h     | OUT2CRTL                                                                                              | Sets toggle and resets Bulk2 OUT endpoint      | W   |  |  |  |

| 03h     | OUT3CRTL Sets toggle and resets Bulk3 OUT endpoint OUT4CRTL Sets toggle and resets Bulk4 OUT endpoint |                                                |     |  |  |  |

| 04h     | OUT4CRTL                                                                                              | Sets toggle and resets Bulk4 OUT endpoint      | W   |  |  |  |

| 05h     | OUT5CRTL                                                                                              | Sets toggle and resets Bulk5 OUT endpoint      | W   |  |  |  |

| 06h     | OUT6CRTL                                                                                              | Sets toggle and resets Bulk6 OUT endpoint      |     |  |  |  |

| 07h     | h OUT7CRTL Sets toggle and resets Bulk7 OUT endpoint                                                  |                                                |     |  |  |  |

| 08h     | 3h OUT8CRTL Sets toggle and resets Interrupt0 OUT endpoint                                            |                                                |     |  |  |  |

| 09h     | OUT9CRTL Sets toggle and resets Interrupt1 OUT endpoint                                               |                                                |     |  |  |  |

| 0Ah     | OUT10CRTL Sets toggle and resets Interrupt2 OUT endpoint                                              |                                                | W   |  |  |  |

| 0Bh     | OUT11CRTL                                                                                             | Sets toggle and resets Interrupt3 OUT endpoint | W   |  |  |  |

| 0Ch     |                                                                                                       | N/A                                            |     |  |  |  |

| 0Dh     |                                                                                                       | N/A                                            |     |  |  |  |

| 0Eh     |                                                                                                       | N/A                                            |     |  |  |  |

| 0Fh     |                                                                                                       | N/A                                            |     |  |  |  |

| 10h     | INOCRTL                                                                                               | Sets toggle and resets BulkO IN endpoint       | W   |  |  |  |

| 11h     | IN1CRTL                                                                                               | Sets toggle and resets Bulk1 IN endpoint       | W   |  |  |  |

| 12h     | IN2CRTL                                                                                               | Sets toggle and resets Bulk2 IN endpoint       | W   |  |  |  |

| 13h     | IN3CRTL                                                                                               | Sets toggle and resets Bulk3 IN endpoint       | W   |  |  |  |

| 14h     | IN4CRTL                                                                                               | Sets toggle and resets Bulk4 IN endpoint       | W   |  |  |  |

| 15h     | IN5CRTL Sets toggle and resets Bulk5 IN endpoint                                                      |                                                |     |  |  |  |

| 16h     | IN6CRTL                                                                                               | Sets toggle and resets Bulk6 IN endpoint       | W   |  |  |  |

| 17h     | IN7CRTL           | Sets toggle and resets Bulk7 IN endpoint                                                    | W   |

|---------|-------------------|---------------------------------------------------------------------------------------------|-----|

| 18h     | IN8CRTL           | Sets toggle and resets Interrupt0 IN endpoint                                               | W   |

| 19h     | IN9CRTL           | Sets toggle and resets Interrupt1 IN endpoint                                               | w   |

| 1Ah     | IN10CRTL          | Sets toggle and resets Interrupt2 IN endpoint                                               | W   |

| 1Bh     | IN11CRTL          | Sets toggle and resets Interrupt3 IN endpoint                                               | w   |

| 1Ch     |                   |                                                                                             |     |

| 1Dh     |                   |                                                                                             |     |

| 1Eh     |                   |                                                                                             |     |

| 1Fh     |                   |                                                                                             |     |

| 20h     | Feature control 0 | Resets and/or clears all Bulk and Interrupt endpoints IN and OUT                            | w   |

| 21h     | Feature control 1 | Resets all Bulk endpoints IN and OUT and/or set all Bulk and Interrupt endpoints IN and OUT | W   |

| 22h     | Feature control 2 | Resets all Bulk OUT and/or clears all Bulk and Interrupt endpoints IN                       | W   |

| 23h     | Feature control 3 | Resets all Bulk IN and/or sets all Bulk and Interrupt endpoints IN                          | W   |

| 24h     | Feature control 4 | Resets all Interrupt endpoints IN and OUT and/or clear all Bulk and Interrupt endpoints OUT |     |

| 25h     | Feature control 5 | Resets all Interrupt endpoints OUT and/or set all Bulk and Interrupt endpoints OUT          | W   |

| 26h     | Feature control 6 | Resets all Interrupt endpoints IN and/or clears all Bulk endpoints IN and OUT               | w   |

| 27h     | Feature control 7 | Resets all Bulk and Interrupt endpoints OUT and/or sets all Bulk endpoints IN and OUT       | W   |

| 28h     | Feature control 8 | Resets all Bulk and Interrupt endpoints IN and/or clears all Interrupt endpoints IN and OUT | W   |

| 29h     | Feature control 9 | Sets all Interrupt endpoints IN and OUT                                                     | w   |

| 30h–3Fh | N/A               |                                                                                             |     |

| 40h     | Status_USB        | Status Register                                                                             | R/W |

| 41h     | DEVICE_addr       | Device address                                                                              | w   |

| 42h     | Test              | Test Settings                                                                               | w   |

| 43h     | Suspend           | Suspend Settings                                                                            | W   |

| 44h     | Valid_in_L        | Valid IN low byte                                                                           | W/R |

| 45H     | Valid_in_H        | Valid IN high byte                                                                          | W/R |

| 46h     | Valid_out_L       | Valid_out low byte                                                                          | W/R |

| 47h     | Valid_out_H       | Valid out high byte                                                                         | W/R |

| 48h     | Stall_in_L        | Stall in low byte                                                                           | W/R |

| 49h     | Stall_in_H        | Stall in High byte                                                                          | W/R |

| 4Ah | Stall_out_L                                      | Stall out Low byte                                                                  | W/R |  |  |

|-----|--------------------------------------------------|-------------------------------------------------------------------------------------|-----|--|--|

| 4Bh | Stall_out_H                                      | Stall out H byte                                                                    | W/R |  |  |

| 4Ch | Int_Enable                                       | Interrupt Enable Register                                                           | W/R |  |  |

| 4Dh |                                                  | N/A                                                                                 |     |  |  |

| 4Eh |                                                  | N/A                                                                                 |     |  |  |

| 4Fh |                                                  | N/A                                                                                 |     |  |  |

| 50h | Max_Pack_size_L_C                                | Max packet size low byte ep 12                                                      | W   |  |  |

| 51h | Max_Pack_size_H_C                                | Max packet size high byte ep 12                                                     | W   |  |  |

| 52h | Max_Pack_size_L_D Max packet size low byte ep 13 |                                                                                     |     |  |  |

| 53h | Max_Pack_size_H_D                                | Max packet size high byte ep 13                                                     | W   |  |  |

| 54h | Max_Pack_size_L_E                                | Max packet size low byte ep 14                                                      | W   |  |  |

| 55h | Max_Pack_size_H_E                                | Max packet size high byte ep 14                                                     | W   |  |  |

| 56h | Max_Pack_size_L_F                                | Max packet size low byte ep 15                                                      | W   |  |  |

| 57h | Max_Pack_size_H_F                                | Max packet size high byte ep 15                                                     | W   |  |  |

| 58h | New_Frm_L                                        | New Frame low byte                                                                  | R   |  |  |

| 59h | New_Frm_H                                        | New Frame high byte                                                                 | R   |  |  |

| 5Ah | Counter_wr_low                                   | Counter_wr low byte. Defines number of bytes send during the contro transfer.       | w   |  |  |

| 5Bh | Counter_wr_high                                  | Counter_wr high byte. Defines number of bytes send during the contro transfer.      | w   |  |  |

| 5Ch | Counter_rd_low                                   | Counter_rd_low byte. Defines number of bytes received during the control transfer.  | R   |  |  |

| 5Dh | Counter_rd_high                                  | Counter rd high byte. Defines number of bytes received during the control transfer. | R   |  |  |

| 5Eh |                                                  | N/A                                                                                 |     |  |  |

| 5Fh |                                                  | N/A                                                                                 |     |  |  |

| 60h | setup 0                                          | Setup byte 0                                                                        | R   |  |  |

| 61h | setup 1                                          | Setup byte 1                                                                        | R   |  |  |

| 62h | setup 2                                          | Setup byte 2                                                                        | R   |  |  |

| 63h | setup 3                                          | Setup byte 3                                                                        | R   |  |  |

| 64h | setup 4                                          | Setup byte 4                                                                        | R   |  |  |

| 65h | setup 5                                          | Setup byte 5                                                                        | R   |  |  |

| 66h | setup 6                                          | Setup byte 6                                                                        | R   |  |  |

| 67h | setup 7                                          | Setup byte 7                                                                        | R   |  |  |

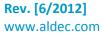

The ALUSB 2.0 core is treated as *target*, however, the microprocessor is treated as *initiator* (see chapter 2.2 of VCI standard). According to VCI standard, the ALUSB 2.0 interface consists of following ports:

- VAL,

- ACK,

- RD,

- ADDRESS(6 downto 0),

- WDATA(7 downto 0).

Since the interface supports only 8-bit data width and supports neither burst transactions nor error signaling, these five ports suffice to perform any read and write operation. The figure 3.2 shows signals used by VCI interface in the ALUSB 2.0.

Figure 0.2 VSIA interface.

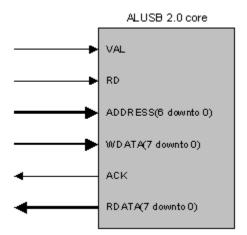

## Write operation

During write operation RD signal is set to 0, microprocessor sets address of register to be written to. Simultaneously, it asserts the VAL signal and updates data on WDATA bus. The address, data and the VAL signal must be maintained until ACK has become asserted and there is a rising edge of CLK. On this edge data are written to ALUSB 2.0 interface.

During write, the ACK is asynchronously generated of VAL. Figure 3.3 shows write operation to the one of registers. Shaded ADDRES and DATA stand for do not care.

Figure 0.3 Write operation to the ALUSB 2.0

The VAL asserted indicates that microprocessor sets address and sets valid data on the bus. ACK asserted means that ALUSB 2.0 core can complete write operation.

#### Note:

ACK is not synchronized to CLK. In write operation ACK depends on VAL only.

If microprocessor meets ACK asserted on rising edge, it should deactivate VAL signal, otherwise the write operation will be performed again.

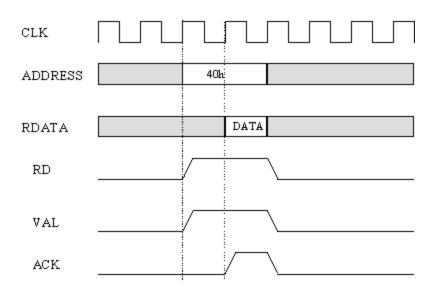

#### **Read operation**

During read operation RD is set to 1, microprocessor sets address of register to be read from. Simultaneously, it asserts the VAL signal. The address, data and the VAL signal must be maintained until ACK has become asserted and there is a rising edge of CLK. During read, the ACK is synchronously generated when VAL is 1 and rising edge on CLOCK occurs. For all registers except for 5Ch and 5Dh, ACK is asserted on next rising edge of CLOCK after VALID is set to 1. For 5Ch and 5Dh registers ACK is asserted two clock cycle after VALID is set to 1. Figure 3.4 shows read operation from Status Register. Shaded ADDRES and DATA stand for do not care.

Figure 0.4 Read operation from Status Register

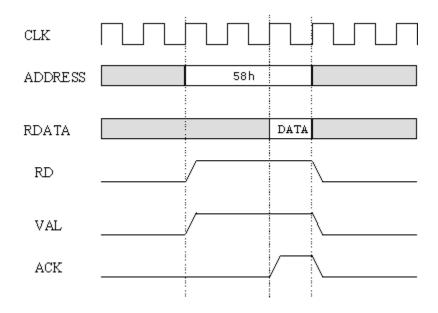

Figure 3.5 shows read operation from New\_Frm\_L register.

Figure 0.5 Read operation from New\_Frm\_L

## **Reading from Status Register**

Status Register is special register that indicates current state of ALUSB 2.0. Status Register is associated with five sources of interrupt generated by the ALUSB 2.0 core. (For more details regarding interrupts see section 11). When any of these interrupts occurs, the INT output is asserted. INT is cleared when all

flags indicating interrupts sources are cleared. In order to clear specified flag in the Status Register, the one should be set to it by writing Status Register with proper mask (See section 11).

The Status register should be read by microprocessor after occurrence of rising edge on INT output.

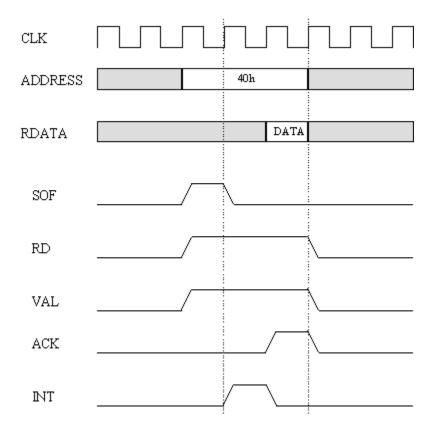

If the read operation is being performed on the Status Register, and some interrupt occurs at the same time, then read operation is postponed. It means that ACK is asserted two or more CLK cycles from VAL set to one. Figure 3.6 shows the case where start of read operation and SOF interrupt occur simultaneously. SOF is internal signal that indicates occurrence of new frame (microframe) (for more detail see section 4).

Figure 0.6 Read operation from Status Register when SOF interrupt occurs

The INT output is asserted one CLOCK cycle after SOF is set to one. ACK is asserted one cycle later. It causes that microprocessor reads Status Register that is updated and information of SOF interrupt is indicated during current read. If no interrupt occurs at the beginning of read operation, the read is performed as shown on figure 3.5.

If any interrupt occurs at the beginning of read operation of the others registers, the read is not postponed.

# **Protocol Management Block**

## Introduction

Because the USB 2.0 devices operate on very high frequency – 480MHz, data recovery cannot be handled using HDL technology. For full-speed devices ASIC vendors provide only simple level translator to meet the USB signaling requirements. This technology is not sufficient for USB 2.0 clock rate. The USB 2.0 transceiver must handle low level USB protocol to provide the data rate that is compatible with today's FPGA devices. Intel<sup>TM</sup> released specification for USB 2.0 transceiver. The UTMI transceiver handles data serialization and deserialization, bit-stuffing and clock recovery and synchronization. The USB data are provided in parallel form and the data rate does not exceed 60MHz. The Aldec USB 2.0 core is designed to interface with the UTMI transceiver. It is capable of transmitting data at both full-speed and high-speed data rates. The pinout conforms with the UTMI specification.

## Interface to UTMI

The UTMI specification provides two interfaces. The 8-bit interface supports 60MHz performance and is intended for ASIC implementation. The UTMI specification provides also 16-bit interface, which is intended for FPGA based designs. The Aldec USB core is compatible with the 16-bit interface. However, the 8-bit UTMI can be also very easy connected. A simple logic must be added between the USB and UTMI interface. The USB core provides global clock enable signal, which can be used in this case to adjust clock frequency of the USB core. The Protocol Management block contains the following signals, which should be connected to the UTMI transceiver:

## Table 0.2 UTMI interface signlas

| Name       | Direction | Active Level | Description                                                                                         |

|------------|-----------|--------------|-----------------------------------------------------------------------------------------------------|

| CLK        | Input     | Rising-Edge  | Global Clock Signal                                                                                 |

| CLKEN      | Input     | High         | Global Clock Enable Signal.                                                                         |

| Reset      | Input     | High         | Global asynchronous reset.                                                                          |

| XcvrSelect | Output    | N/A          | Transceiver Select – selects HS/FS transceiver.                                                     |

| TermSelect | Output    | N/A          | Termination Select – selects HS/FS termination.                                                     |

| SuspendM   | Output    | Low          | Suspend UTMI transceiver – macrocell circuitry drawing suspend current.                             |

| LineState  | Output    | N/A          | Line State – reflects the current state of the single ended receivers.                              |

| (0-1)      |           |              |                                                                                                     |

| OpMode     | Output    | N/A          | Operational Mode – select operation mode for UTMI transceiver.                                      |

| (0-1)      |           |              |                                                                                                     |

| DataOut    | Output    | N/A          | DataOut – 16-bit parallel data bus.                                                                 |

| (0-15)     |           |              |                                                                                                     |

| TXValid    | Output    | High         | Transmit Valid – indicates that the DataOut bus is valid.                                           |

| TXValidH   | Output    | High         | Transmit Valid High – indicates that DataOut(8-15) bus is valid.                                    |

| TXReady    | Input     | High         | Transmit Data Ready – indicates that UTM will load data from DataOut bus on the rising edge of CLK. |

| DataIn     | Input     | N/A          | DataIn – 16-bit parallel data bus.                                                                  |

| (0-15)     |           |              |                                                                                                     |

| RXValid    | Input     | High         | Receive Data Valid – indicates that DataIn bus has valid data.                                      |

| RXValidH   | Input     | High         | Receive Data Valid H – indicates that DataIn(8-15) bus has valid data.                              |

| RXActive   | Input     | High         | Receive Active – indicates that SYNC has been detected and UTM starts receiving data.               |

| nUSBRes    | Input     | Low          | Reset for Kawasaki transceiver.                                                                     |

The UTMI interface is defined in the "USB 2.0 Transceiver Macrocell Interface Specification" provided by  $Intel^{TM}$ . The specification contains details about functionality and timing of the interface. The UTMI transceiver handles the following functions:

- Data and clock recovery from serial stream on the USB.

- SYNC/EOP generation and checking.

- Bit-stuffing, unstuffing and bit-stuff error detection.

- Suspend/Resume signaling.

- USB 2.0 Test Mode.

The data received from USB cable are deserialized. The UTMI block removes suffed bits and SYNC and EOP fields from the USB packet. The PID and CRC fields remain unchanged. Then, the data are outputted using parallel interface. The UTM interface handles additionally Suspend, Reset and Resume signaling. The UTMI logic allows us to detect or send Chirp K, J states on the USB bus. The High-Speed or Full-Speed operation mode can be changed any time to handle Suspend or Resume signaling.

The USB core contains nUSBRes additional port. It is reset signal for Kawasaki KL5KUSB200 transceiver. The KL5KUSB200 chip is not fully compliant with UTMI specification. It requires asynchronous resetting while the USB Host performs bus reset signaling. The nUSBRes port should be connected directly with RSTN input of the KL5KUSB200 transceiver. Please, refer to KL5KUSB200 USB 2.0 compliant Transceiver Chip DataSheet Rev 0.21 for additional information. The nUSBRes signal is active by 330ns at the beginning of each USB bus reset sequence. It resets asynchronously the KL5KUSB200 transceiver and remains inactive until the next bus reset sequence. This port should be left unconnected while other UTMI transceivers are used.

# **USB Packets Decoding**

The Protocol Management Block receives data form UTMI transceiver. First of all this block must find out what packet type is being sent by the USB bus. The packet identifier (PID) is decoded to determine the type of packet, the format of the packet and the tape of error detection applied to the packet. If the packet has a CRC filed the protocol management unit performs CRC checking. The packet is considered invalid if CRC checking fails. The packets are divided into four groups:

- Token packets.

- Data packets.

- Handshake packets.

- Special packets.

Each token packet excluding SOF contains address filed and endpoint filed.

If such token packet is received the protocol management unit checks the address field to determine if the token is addressed to its. If address checking fails the token is ignored. Otherwise, the endpoint field is decoded and corresponding endpoint manager is informed that following transaction is addressed to its.

The SOF packet is addressed to all possible USB devices connected to the bus. The SOF token consists of a PID and 11-bit frame number. The SOF token must be delivered once to all USB devices every 1ms for full-speed bus or every 125us for high-speed bus. If SOF token was corrupted due to bus errors, the USB device must synthesize existence of the damaged SOF. The protocol management unit performs all these operations. The ISO endpoints managers are informed if valid SOF PID was received. The frame number register is updated if SOF token was received and CRC sum is correct. The protocol management unit generates also the damaged SOFs. The contents of the frame number registers is shown the tabes below

New\_Frm\_L X58 New Frame Low Byte b7 b6 b5 b4 b3 b2 b1 b0 Frm2 Frm1 Mfr 2 Mfr 1 Mfr0 Frm4 Frm3 Frm0 R R R R R R R R 0 0 0 0 0 0 0 0

Table 0.3 New Frame Low byte register

Table 0.4 New Frame High Byte

| New_Frm_H |    | New Frame | High Byte | X59  |      |      |      |

|-----------|----|-----------|-----------|------|------|------|------|

| b7        | b6 | b5        | b4        | b3   | b2   | b1   | b0   |

| -         | -  | Frm10     | Frm9      | Frm8 | Frm7 | Frm6 | Frm5 |

| R         | R  | R         | R         | R    | R    | R    | R    |

| 0         | 0  | 0         | 0         | 0    | 0    | 0    | 0    |

The three last significant bits contain the microframe number. These bits are reset to zero and remain unchanged if device works in full-speed mode.

A data packet consists of a PID, a data filed containing zero or more data bytes and CRC. The protocol management unit checks and removes the PID and CRC fields and moves the data to the endpoints managers. Each endpoint manager is informed what type of PID was received in current data packet. If an endpoint manager sends data the protocol management unit moves the data to UTMI transceiver and calculates CRC sum. The CRC sum is added at the end of the packet.

All special packets are ignored by USB function device excluding PING token. The PING token is handled similarly like other token packets. The protocol management block sends information to corresponding bulk manager that PING token was received.

Handshake packets consist of only a PID. The protocol management unit sends information to all endpoints managers if this packet was received.

# **Reset Signaling**

If the USB function device works in HS mode and detects bus inactivity for more than 3ms then operation mode must be switched to full-speed. Then the protocol management block checks the LineState signals for SEO condition. If SEO is asserted the protocol management block forces reset sate to the device. If the USB function device operates in full-speed mode and sees an SEO on its port for more than 2.5us treats this signal as a reset. If the reset was detected then device performs HS detection handshake protocol. The device sends Chirp-K on the bus and waits for an alternating sequence of Chirp-K and Chirp-J, which should be sent by a hub. If the device detects the chirp sequence then enters high-speed mode, otherwise remains in full-speed mode. The protocol management block sets HsFs flag in the Status Register if high-speed mode is detected. The status register contains USBReset flag. This flag is set to one if device is in the reset state. The USB function device may generate an interrupt if the USBReset flag is set. The interrupt must be enabled setting corresponding bit in the Interrupt Enable Register. Please, refer to the "Registers" section of this document.

Table 0.5 Status Register

| Status_USB |      | Status Regi | ster        | x40 |         |            |          |

|------------|------|-------------|-------------|-----|---------|------------|----------|

| b7         | b6   | b5          | b4          | b3  | b2      | b1         | b0       |

| EnumEnable | HsFs | Resume      | SetDataIntr | SOF | TkSetup | SuspDetect | UsbReset |

| W          | R    | R           | R/W         | R/W | R/W     | R/W        | R/W      |

| 0          | 0    | 0           | 0           | 0   | 0       | 0          | 0        |

# Suspend and Resume signaling

If HS device detects SE0 asserted on the bus for more than 3ms then the operation mode is switched to full-speed. After that, the protocol management block checks the LineState signals for an 'J' state. If the 'J' state is asserted by time longer than 100us the device enters suspend state. The FS device goes into the suspend state after it sees a constant 'J' state for more than 3ms. After detecting the suspend signaling the USB core alerts external microcontroller by setting SuspDetect flag in the Status Register. This may cause generation of an interrupt if corresponding enable flag is set to one in the Interrupt Enable register. The microcontroller responds to the interrupt by performing any necessary operation as shutting off external power consuming devices. Next, the microcontroller sets the EnterSusp flag in the Suspend register. After that, the USB Core drives the Suspend pin to one. The high state on the Suspend pin should turn off the external clock oscillator. These actions put the USB core into low power mode, as required by the USB specification.

Table 0.6 Suspend Register

| Suspend |    | Suspend Re | gister | x43 |           |          |          |

|---------|----|------------|--------|-----|-----------|----------|----------|

| В7      | b6 | B5         | b4     | b3  | b2        | b1       | b0       |

| D7      | D6 | D5         | D4     | D3  | EnterSusp | ResumeEn | DriveRes |

| R       | R  | R          | R      | R   | R/W       | R/W      | R/W      |

| 0       | 0  | 0          | 0      | 0   | 0         | 0        | 0        |

If a device is in the suspend state, its operations are resumed when any non-idle signaling is received on its upstream facing port. The device can also generate resume signaling to resume system operation if its remote wakeup capability, has been enabled by the USB host. Resume signaling always take place in FS mode, so the behavior for HS device is identical to a FS device. The protocol management block uses the LineState signals to determine when the transition from the 'J' to the 'K' state occurs.

If a non-idle state occurred on the bus, the USB core clears the Suspend pin and sets Resume flag in the Status Register. The external clock oscillator should restart its operation. The Resume flag can also generate an interrupt for external microcontroller. After these actions the USB device continues operation in the same speed mode, which was before suspending.

An event internal to the device may initiate the resume process (Remote Wakeup). The USB device must report that it is capable of signaling remote wakeup in the configuration descriptor. The remote wakeup is possible if the USB host enabled the remote wakeup capability by sending Set Feature/Device

request. The ResumeEn bit in the Suspend register should be set to one if the remote wakeup is enabled. The microcontroller or the Enumeration Manager can set this bit in response to the Set Feature/Device request. Assuming that ResumeEn bit is set, the microcontroller can set DriveRes bit in the Suspend register to drive remote wakeup. This signal must be asserted for at last 1ms. After this time the USB host performs all necessary operation to wake up system and start transmission on the bus.

## **USB 2.0 Test Mode Generation**

Test mode of a port is entered using a device specific standard request. The microcontroller or the Enumeration Manager must enter the test mode in response to the SetFeature(Test Mode) request. The USB Core supports the following test modes:

| Test Type    | Test Number | Description                                                        |

|--------------|-------------|--------------------------------------------------------------------|

| Test_J       | 01h         | The USB core sends continuously the high-speed J state on the bus. |

| Test_K       | 02h         | The USB core sends continuously the high-speed K state on the bus. |

| Test_SE0_NAK | 03h         | The USB core responds to any IN token packet with a NAK handshake. |

| Test_Packet  | 04h         | The USB core sends the test packet.                                |

The USB core contains the Test Mode register. The register consists of the test number bits and the test enable flag. The microcontroller sets the appropriate test mode on the four last significant bits of the registers. The list of available test modes is shown in the table above. If the test number was set properly, the microcontroller enables the test by setting the TestEN flag. The protocol management block performs all operation required by selected test. The test can be disabled by resetting the USB device.

Table 0.7 Test Mode register

| TestMode |    | Test Mode |        |         |         | X42     |         |

|----------|----|-----------|--------|---------|---------|---------|---------|

| b7       | b6 | b5        | b4     | b3      | b2      | b1      | b0      |

| D7       | D6 | D5        | TestEN | TestNR3 | TestNr2 | TestNr1 | TestNr0 |

| R        | R  | R         | R/W    | R/W     | R/W     | R/W     | R/W     |

| 0        | 0  | 0         | 0      | 0       | 0       | 0       | 0       |

The Enumeration Manager may also select and run these tests if it was enabled to handle the enumeration process. The microcontroller does not have access to the register if the enumeration manager is enabled.

# **Enumeration Management block.**

# **Control Endpoint Zero**

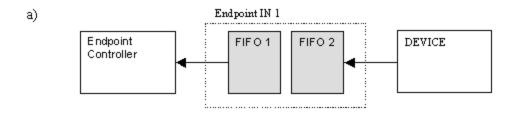

The endpoint zero is a control endpoint and is required by every USB device. The endpoint accepts setup tokens and receives standard device requests. The control endpoint zero is defined by the USB specification as one bidirectional endpoint. The endpoint was implemented as two bulk IN and OUT endpoints in Aldec USB Core. Both of these endpoints are handled as normal bulk endpoints. The division of the control endpoint into two separate endpoints does not affect any control transaction. The control endpoint zero cooperates with the Enumeration Manager, which receives the setup packets. The setup data are never loaded to endpoint's zero buffers. The Enumeration Manager transfers the eight-byte packet to local data buffer for further processing. The setup packet is always received and acknowledged regardless of the control endpoint's valid, busy or stall bits. The setup packets contain an eight-byte data structure that provides information about the device request. The 8-byte buffer holds data that arrives in setup stage of the control transfer. The setup data can be processed by a microcontroller or by the Enumeration Manager. It depends on the EnumEnable flag in the Status Register.

| Status_USB |      | Status Register |             |     |         | x40        |          |

|------------|------|-----------------|-------------|-----|---------|------------|----------|

| b7         | b6   | b5              | b4          | b3  | b2      | b1         | b0       |

| EnumEnable | HsFs | Resume          | SetDataIntr | SOF | TkSetup | SuspDetect | UsbReset |

| R/W        | R    | R               | R/W         | R/W | R/W     | R/W        | R/W      |

| 1          | 0    | 0               | 0           | 0   | 0       | 0          | 0        |

Table 0.8 Status Register

If the flag is set to one the Enumeration Manager handles all standard USB requests. Otherwise, the microcontroller must interpret the 8-byte packet and respond to the request.

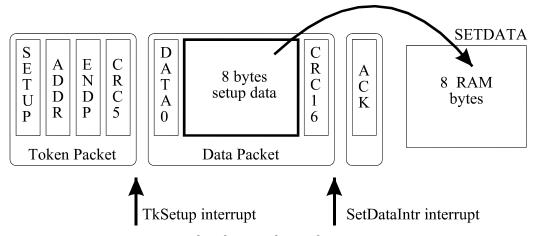

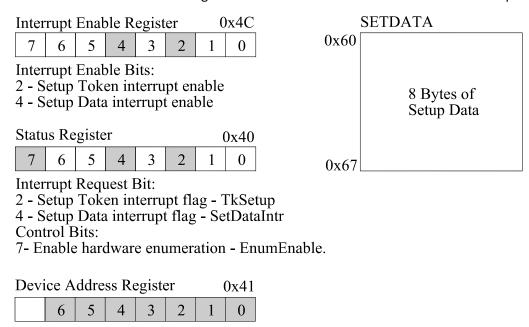

The USB core generates separate interrupt requests for the various control transfer phases, as shown on the figure below. These interrupt are generated to simplify handling the USB request.

Figure 0.7 Interrupts associated with control transfer

The USB core generates TkSetup (Setup Token Arrived) interrupt when setup token was received. This interrupt is normally used for configuration of control endpoint zero. The microcontroller can set toggle bits and disarm the endpoint to be ready for data stage and status stage of the control transaction. The USB core generates SetDataIntr (Setup Data Arrived) interrupt when the eight bytes of setup data have been received error-free and transferred to local buffer starting at address SETDATA (0x60).

A microcontroller program responds to the SetDataIntr interrupt by inspecting the eight bytes of setup data. When the processing is finished the microcontroller arms the control endpoint to handle data stage or status stage of the control transaction.

The figure below shows the set of USB registers that deal with control transactions over endpoint zero.

Figure 0.8 Registers for Handling Setup Transactions

Two bits in the Interrupt Enable Register enable the Setup Token and Setup Data interrupts. The USB core transfers eight setup bytes into the RAM buffer at SETDATA address. The Status register contains EnumEnable control bit. The Device Address Register contains USB device address. This register can be changed in response to Set Address request. The microcontroller may need access to the Stall and Valid registers to handle some request regarding bulk endpoints. Please, refer to the "Registers" section of this document for detailed description of these registers.

# **Enumeration Manager**

The USB core contains the Enumeration Manager block to perform enumeration without external microcontroller. The Enumeration Manager contains the USB descriptors. This block sets the proper endpoint configuration bits to match the descriptors. The USB core handles all device requests over control endpoint zero, so the developer can immediately start writing code to transfer data over USB using these preconfigured endpoints. The enumeration process can be handled also by the external microcontroller.

The EnumEnable bit in the Status Register determines which entity the core or the microcontroller handles enumeration process. At power on the EnumEnable bit is one, indicating that the USB core

handles device requests. The Table below shows how the USB core responds to USB request when EnumEnable=1.

Table 0.9 USB Device Requests

| Request                | Action                                         |

|------------------------|------------------------------------------------|

| Get Descriptor         | Supplies table of descriptors                  |

| Get Configuration      | Return configuration number                    |

| Get Interface          | Return Alternate Settings number               |

| Get Status/Device      | Return two zero bytes                          |

| Get Status/Interface   | Return two zero bytes                          |

| Get Status/Endpoint    | Supplies Stall bit for indicated EP            |

| Clear Feature/Device   | None                                           |

| Clear Feature/Endpoint | Clears Stall bit for indicated EP              |

| Set Feature/Device     | None                                           |

| Set Feature/Endpoint   | Set Stall bit for indicated endpoint           |

| Set Configuration      | Configure device and sets configuration number |

| Set Interface          | Configure device and sets interface number     |

| Set Address            | Set device address                             |

| Set Descriptor         | None                                           |

| Sync Frame             | None                                           |

The USB core has built-in descriptor data table. The Enumeration Manager sends the descriptor table in response to Get Descriptor request. The USB device consists of single USB configuration containing one interface with two alternate setting. The endpoints reported for this device are shown in the table below:

Table 0.10 The USB Core Endpoints

| Endpoint | Туре      | Alternate S     | Settings |

|----------|-----------|-----------------|----------|

|          | <b>'</b>  | 0               | 1        |

|          |           | Max Packet Size |          |

| 0 INOUT  | CTRL      | 64              | 64       |

| 1 IN     | Bulk      | 0               | 64       |

| 1 OUT    | Bulk      | 0               | 64       |

| 2 IN     | Bulk      | 0               | 64       |

| 2 OUT    | Bulk      | 0               | 64       |

| 3 IN     | Bulk      | 0               | 64       |

| 3 OUT    | Bulk      | 0               | 64       |

| 4 IN     | Bulk      | 0               | 64       |

| 4 OUT    | Bulk      | 0               | 64       |

| 5 IN     | Bulk      | 0               | 64       |

| 5 OUT    | Bulk      | 0               | 64       |

| 6 IN     | Bulk      | 0               | 64       |

| 6 OUT    | Bulk      | 0               | 64       |

| 7 IN     | Bulk      | 0               | 64       |

| 7 OUT    | Bulk      | 0               | 64       |

| 8 IN     | Interrupt | 0               | 64       |

| 8 OUT    | Interrupt | 0               | 64       |

| 9 IN     | Interrupt | 0               | 64       |

| 9 OUT    | Interrupt | 0               | 64       |

| 10 IN    | Interrupt | 0               | 64       |

| 10 OUT   | Interrupt | 0               | 64       |

| 11 IN    | Interrupt | 0               | 64       |

| 11 OUT   | Interrupt | 0               | 64       |

| 12 IN    | ISO       | 0               | 64       |

| 12 OUT   | ISO       | 0               | 64       |

| 13 IN    | ISO       | 0               | 64       |

| 13 OUT   | ISO       | 0               | 64       |

| 14 IN  | ISO | 0 | 64 |

|--------|-----|---|----|

| 14 OUT | ISO | 0 | 64 |

| 15 IN  | ISO | 0 | 64 |

| 15 OUT | ISO | 0 | 64 |

The alternate setting zero uses no interrupt or isochronous bandwidth as recommended by USB specification. If the Enumeration Manager is turned on the microcontroller may also read or write the endpoint's STALL registers. The microcontroller may have to halt an endpoint because of receiving incorrect data. The Enumeration Manager has a higher priority if both microcontroller and the Enumeration Manager write data to the register at the same time. The Enumeration Manager controls also Device Address Register. The microcontroller may write data to the register but the data are ignored as long as the EnumEnable bit is one. If the EnumEnable bit is reset to zero, the USB core passes all USB request onto the microcontroller via the SETDATA buffer. The STALL registers and Device Address register are fully controlled by the microcontroller if EnumEnable is reset to zero.

#### Note:

The USB configuration can be changed upon user request. Some of endpoints can be removed and the USB descriptors can by modified to meet user requirements.

# **USB Requests**

The USB specification defines a set of Standard Device Requests. The request and the request's parameters are sent to the device in the setup packet. Every setup packet has eight bytes. USB device must respond to standard device request. This section describes how the USB device responds to individual request.

## **Get Status Request.**

The USB specification defines three USB status requests. The requests are as follows:

- 1. Decvice Staus

- a. Remote Wakeup

- b. Self-Powered

- 2. Endpoint Staus

- a. Stall bit.

- 3. Interface Status reserved.

The following tables show the eight setup bytes for the Get Status request:

# Table 0.11 Get Device Status Request

| Byte | Field     | Value | Description                 | Response            |

|------|-----------|-------|-----------------------------|---------------------|

| 0    | bmRequest | 0x80  | Request to device - type In | Byte 0:             |

| 1    | bRequest  | 0x00  | Get Status request          | Bit0 – Self Powered |

| 2    | wValueL   | 0x00  |                             | Bit1- Remote Wakeup |

| 3    | wValueH   | 0x00  |                             |                     |

| 4    | wIndexL   | 0x00  |                             | Byte 1: zero        |

| 5    | wIndexH   | 0x00  |                             |                     |

| 6    | wLengthL  | 0x02  | Two bytes must be returned  |                     |

| 7    | wLengthH  | 0x00  |                             |                     |

# Table 0.12 Get Interface Status Request

| Byte | Field     | Value | Description                    | Response    |

|------|-----------|-------|--------------------------------|-------------|

| 0    | bmRequest | 0x81  | Request to interface - type In | Byte0: zero |

| 1    | bRequest  | 0x00  | Get Status request             |             |

| 2    | wValueL   | 0x00  |                                | Byte1: zero |

| 3    | wValueH   | 0x00  |                                |             |

| 4    | wIndexL   | INTR  | Interface number               |             |

| 5    | wIndexH   | 0x00  |                                |             |

| 6    | wLengthL  | 0x02  | Two bytes must be returned     |             |

| 7    | wLengthH  | 0x00  |                                |             |

# Table 0.13 Get Endpoint Status request

| Byte | Field     | Value | Description                   | Response         |

|------|-----------|-------|-------------------------------|------------------|

| 0    | bmRequest | 0x82  | Request to Endpoint - type In | Byte0:           |

| 1    | bRequest  | 0x00  | Get Status request            | Bit0 – Stall bit |

| 2    | wValueL   | 0x00  |                               |                  |

| 3    | wValueH   | 0x00  |                               | Byte1: zero      |

| 4    | wIndexL   | EP    | Endpoint number               |                  |

| 5    | wIndexH   | 0x00  |                               |                  |

| 6    | wLengthL  | 0x02  | Two bytes must be returned    |                  |

| 7    | wLengthH  | 0x00  |                               |                  |

The Get Status Device request queries the state of two bits, Remote Wakup and Self-Powered. The Remote Wakeup bit indicates whether or not the device is enabled to request remote wakeup. The Self-powered bit indicates whether or not the device is self-powered.

The Enumeration Manager returns two zero bytes in response to Get Status Interface request. This request is reserved for future use.

Each bulk or interrupt endpoint has a Stall bit. If this bit is set the endpoint returns a STALL handshake in response to any USB transaction. The Get Status Endpoint request returns the Stall bit for corresponding endpoint.

## **Get Configuration Request.**

Table 0.14 Get Configuration Request

| Byte | Field     | Value | Description                 | Response                 |

|------|-----------|-------|-----------------------------|--------------------------|

| 0    | bmRequest | 0x80  | Request to device - type In | Byte 0:                  |

| 1    | bRequest  | 0x08  | Get Configuration Request   | The configuration number |

| 2    | wValueL   | 0x00  |                             |                          |

| 3    | wValueH   | 0x00  |                             |                          |

| 4    | wIndexL   | 0x00  |                             |                          |

| 5    | wIndexH   | 0x00  |                             |                          |

| 6    | wLengthL  | 0x01  | One bytes must be returned  |                          |

| 7    | wLengthH  | 0x00  |                             |                          |

The Enumeration Manager returns the current configuration number in response to this request.

## **Get Interface Request**

Table 0.15 Get Interface Request

| Byte | Field     | Value | Description                 | Response                                      |

|------|-----------|-------|-----------------------------|-----------------------------------------------|

| 0    | bmRequest | 0x81  | Request to Device - type In | Byte 0:                                       |

| 1    | bRequest  | 0x0A  | Get Interface Request       | The alternate Setting for specified interface |

| 2    | wValueL   | 0x00  |                             | specified interface                           |

| 3    | wValueH   | 0x00  |                             |                                               |

| 4    | wIndexL   | INTR  | Interface Number            |                                               |

| 5    | wIndexH   | 0x00  |                             |                                               |

| 6    | wLengthL  | 0x01  | One bytes must be returned  |                                               |

| 7    | wLengthH  | 0x00  |                             |                                               |

The Enumeration Manager returns the alternate setting for selected interface.

# **Get Descriptor Request**

The USB specification defines four types of the Get Descriptor request:

- Get Descriptor Device

- Get Descriptor Configuration

- Get Descriptor Device Qualifier

- Get Descriptor Other Speed Configuration

The following tables show the setup packet bytes for the Get Descriptor requests:

Table 0.16 Get Device Descriptor Request

| Byte | Field     | Value | Description                 | Response |        |            |

|------|-----------|-------|-----------------------------|----------|--------|------------|

| 0    | bmRequest | 0x80  | Request to Device - type In | The      | Device | descriptor |

| 1    | bRequest  | 0x06  | Get Descriptor request      | table.   |        |            |

| 2    | wValueL   | 0x00  |                             |          |        |            |

| 3    | wValueH   | 0x01  | Device Descriptor           |          |        |            |

| 4    | wIndexL   | 0x00  |                             |          |        |            |

| 5    | wIndexH   | 0x00  |                             |          |        |            |

| 6    | wLengthL  | LenL  | Number of returned bytes    |          |        |            |

| 7    | wLengthH  | LenH  |                             |          |        |            |

# Table 0.17 Get Configuration Descriptor Request.

| Byte | Field     | Value | Description                 | Response          |

|------|-----------|-------|-----------------------------|-------------------|

| 0    | bmRequest | 0x80  | Request to Device - type In | The Configuration |

| 1    | bRequest  | 0x06  | Get Descriptor request      | descriptor table. |

| 2    | wValueL   | CFG   | Configuration number        |                   |

| 3    | wValueH   | 0x02  | Configuration Descriptor    |                   |

| 4    | wIndexL   | 0x00  |                             |                   |

| 5    | wIndexH   | 0x00  |                             |                   |

| 6    | wLengthL  | LenL  | Number of returned bytes    |                   |

| 7    | wLengthH  | LenH  |                             |                   |

Table 0.18 Get Device Qualifier Descriptor Request

| Byte | Field     | Value | Description                 | Response             |

|------|-----------|-------|-----------------------------|----------------------|

| 0    | bmRequest | 0x80  | Request to Device - type In | The Device Qualifier |

| 1    | bRequest  | 0x06  | Get Descriptor request      | descriptor table.    |

| 2    | wValueL   | 0x00  |                             |                      |

| 3    | wValueH   | 0x06  | Device Qualifier Descriptor |                      |

| 4    | wIndexL   | 0x00  |                             |                      |

| 5    | wIndexH   | 0x00  |                             |                      |

| 6    | wLengthL  | LenL  | Number of returned bytes    |                      |

| 7    | wLengthH  | LenH  |                             |                      |

## Table 0.19 Get Configuration Descriptor Request

| Byte | Field     | Value | Description                          | Response                        |

|------|-----------|-------|--------------------------------------|---------------------------------|

| 0    | bmRequest | 0x80  | Request to Device - type In          | The Other speed                 |

| 1    | bRequest  | 0x06  | Get Descriptor request               | configuration descriptor table. |

| 2    | wValueL   | 0x00  |                                      |                                 |

| 3    | wValueH   | 0x07  | Other Speed Configuration Descriptor |                                 |

| 4    | wIndexL   | 0x00  |                                      |                                 |

| 5    | wIndexH   | 0x00  |                                      |                                 |

| 6    | wLengthL  | LenL  | Number of returned bytes             |                                 |

| 7    | wLengthH  | LenH  |                                      |                                 |

The requests return the specified descriptor. The wLength filed specifies the number of bytes to return. A request for configuration descriptor returns the configuration descriptor, all interface descriptors and all endpoint descriptors for all of the interfaces in a single request.

## **Set Address Request**

This request sets the device address for all future device accesses.

Table 0.20 Set Device Address request

| Byte | Field     | Value | Description                  | Response |

|------|-----------|-------|------------------------------|----------|

| 0    | bmRequest | 0x00  | Request to Device - type Out |          |

| 1    | bRequest  | 0x05  | Set Address request          |          |

| 2    | wValueL   | ADDR  | Device Address               |          |

| 3    | wValueH   | 0x00  |                              |          |

| 4    | wIndexL   | 0x00  |                              |          |

| 5    | wIndexH   | 0x00  |                              |          |

| 6    | wLengthL  | 0x00  |                              |          |

| 7    | wLengthH  | 0x00  |                              |          |

# **Set Interface Request**

Some USB devices have configurations with different interfaces and alternate settings. This request allows the host to select an interface and an alternate setting.

Table 0.21 Set Interface request

| Byte | Field     | Value | Description                     | Response |

|------|-----------|-------|---------------------------------|----------|

| 0    | bmRequest | 0x01  | Request to Interface - type Out |          |

| 1    | bRequest  | 0x0B  | Set Interface request           |          |

| 2    | wValueL   | AS    | Alternate Setting               |          |

| 3    | wValueH   | 0x00  |                                 |          |

| 4    | wIndexL   | INTR  | Interface                       |          |

| 5    | wIndexH   | 0x00  |                                 |          |

| 6    | wLengthL  | 0x00  |                                 |          |

| 7    | wLengthH  | 0x00  |                                 |          |

# **Set Configuration Request**

Table 0.22 Set Configuration request

| Byte | Field     | Value | Description                  | Response |

|------|-----------|-------|------------------------------|----------|

| 0    | bmRequest | 0x00  | Request to Device - type Out |          |